# A Survey of Multiprocessor Operating System Kernels (DRAFT)

Bodhisattwa Mukherjee (bodhi@cc.gatech.edu) Karsten Schwan (schwan@cc.gatech.edu) Prabha Gopinath (gopinath\_prabha@ssdc.honeywell.com)

#### GIT-CC-92/05

5 November 1993

## Abstract

Multiprocessors have been accepted as vehicles for improved computing speeds, cost/performance, and enhanced reliability or availability. However, the added performance requirements of user programs and functional capabilities of parallel hardware introduce new challenges to operating system design and implementation.

This paper reviews research and commercial developments in multiprocessor operating system kernels from the late 1970's to the early 1990's. The paper first discusses some common operating system structuring techniques and examines the advantages and disadvantages of using each technique. It then identifies some of the major design goals and key issues in multiprocessor operating systems. Issues and solution approaches are illustrated by review of a variety of research or commercial multiprocessor operating system kernels.

> College of Computing Georgia Institute of Technology Atlanta, Georgia 30332–0280

## Contents

| 1 | 1 Introduction |                                                                    |    |

|---|----------------|--------------------------------------------------------------------|----|

| 2 | Stru           | acturing an Operating System                                       | 4  |

|   | 2.1            | Monolithic Systems                                                 | 4  |

|   | 2.2            | Capability Based Systems                                           | 4  |

|   | 2.3            | Message Passing Systems                                            | 6  |

|   | 2.4            | Language Based Mechanisms                                          | 7  |

|   | 2.5            | Object-Oriented and Object-Supporting Operating Systems            | 8  |

|   | 2.6            | Vertical and Horizontal Organizations                              | 9  |

|   | 2.7            | Micro-kernel Based Operating Systems                               | 10 |

|   | 2.8            | Application-specific Operating Systems                             | 11 |

| 3 | Des            | ign Issues                                                         | 12 |

|   | 3.1            | Processor Management and Scheduling                                | 12 |

|   |                | 3.1.1 Heavyweight Processes to Lightweight Threads                 |    |

|   |                | 3.1.2 Scheduler Structures                                         | 14 |

|   |                | 3.1.3 Scheduling Policies                                          | 14 |

|   | 3.2            | Memory Management                                                  | 19 |

|   |                | 3.2.1 Shared Virtual Memory                                        |    |

|   |                | 3.2.2 NUMA and NORMA Memory Management                             |    |

|   | 3.3            | Synchronization                                                    | 23 |

|   |                | 3.3.1 Locks                                                        | 24 |

|   |                | 3.3.2 Other Synchronization Constructs                             | 26 |

|   | 3.4            | Interprocess Communication                                         | 26 |

|   |                | 3.4.1 Basic Communication Primitives                               | 26 |

|   |                | 3.4.2 Remote Procedure Calls                                       | 27 |

|   |                | 3.4.3 Object Invocations on Shared and Distributed Memory Machines | 28 |

| 4 | San            | ple Multiprocessor Operating System Kernels                        | 28 |

|   |                | HYDRA                                                              | 28 |

|   |                | 4.1.1 Execution Environment and Processes                          |    |

|   |                | 4.1.2 Objects and Protection                                       |    |

|   |                | 4.1.3 HYDRA and Parallel Computing                                 |    |

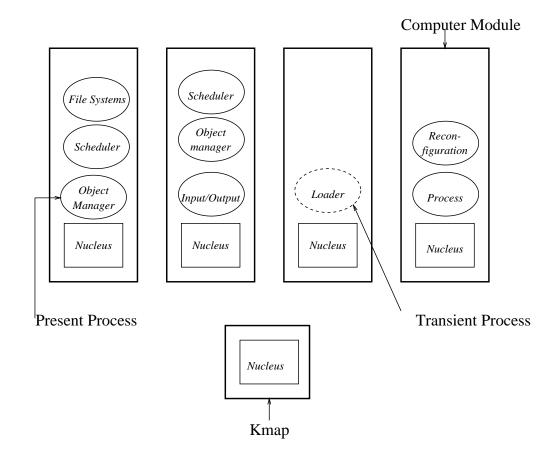

|   | 4.2            | StarOS                                                             |    |

|   |                | 4.2.1 Task Forces                                                  |    |

|   |                | 4.2.2 Synchronization and Communication                            |    |

|   |                | 4.2.3 Scheduling                                                   |    |

|   |                | 4.2.4 Reconfiguration                                              |    |

|   | 4.3            | Mach                                                               |    |

|   |                |                                                                    | -  |

| 4.3.1 Memory Management                                |  |  |  |

|--------------------------------------------------------|--|--|--|

| 4.3.2 Interprocess Communication                       |  |  |  |

| 4.3.3 Scheduling                                       |  |  |  |

| 4.3.4 The Mach 3.0 Micro-kernel                        |  |  |  |

| 4.4 Elmwood                                            |  |  |  |

| 4.4.1 Objects and LONS                                 |  |  |  |

| 4.4.2 Processes and Synchronization                    |  |  |  |

| 4.4.3 Interprocess Communication                       |  |  |  |

| 4.5 Psyche                                             |  |  |  |

| 4.5.1 Synchronization 40                               |  |  |  |

| 4.5.2 Memory Management 41                             |  |  |  |

| 4.5.3 Scheduling                                       |  |  |  |

| 4.6 PRESTO                                             |  |  |  |

| 4.6.1 Customization                                    |  |  |  |

| 4.7 KTK                                                |  |  |  |

| 4.8 Choices                                            |  |  |  |

| 4.8.1 Tasks and Threads                                |  |  |  |

| 4.8.2 Interprocess Communication                       |  |  |  |

| 4.8.3 Memory Management 46                             |  |  |  |

| 4.8.4 Persistent Objects                               |  |  |  |

| 4.8.5 Exception Handling                               |  |  |  |

| 4.9 Renaissance                                        |  |  |  |

| 4.9.1 Process Management                               |  |  |  |

| 4.9.2 Synchronization                                  |  |  |  |

| 4.10DYNIX                                              |  |  |  |

| 4.10.1 Process Management and Scheduling               |  |  |  |

| 4.10.2 Synchronization                                 |  |  |  |

| 4.10.3 Memory Management 48                            |  |  |  |

| 4.11UMAX                                               |  |  |  |

| 4.11.1 Process Management and Scheduling               |  |  |  |

| 4.11.2Synchronization                                  |  |  |  |

| 4.11.3 Memory Management 48                            |  |  |  |

| 4.12 Chrysalis                                         |  |  |  |

| 4.12.1 Process Management and Scheduling               |  |  |  |

| 4.12.2 Memory Management 49                            |  |  |  |

| 4.12.3Synchronization                                  |  |  |  |

| 4.13RP3                                                |  |  |  |

| 4.13.1 Process Management and Scheduling               |  |  |  |

| 4.13.2 Memory Management 50                            |  |  |  |

| 4.14 Operating Systems for Distributed Memory Machines |  |  |  |

### 5 Conclusions and Future Work

## **1** Introduction

Parallel processing has become the premier approach for increasing the computational power of modern supercomputers, in part driven by large-scale scientific and engineering applications like weather prediction, materials and process modeling, and others, all of which require GigaFlop computing speeds and Terabytes of rapidly accessible primary and secondary storage. However, perhaps more important than the HPCC applications named above are commercial motivations for the development of parallel machines, which include improved machine cost/performance, scalability to different application requirements, and enhanced reliability or availability.

The purpose of this survey is to review some of the major concepts in operating systems for parallel machines, roughly reflecting the state of the art in the early 1990's. More importantly, we identify the main research issues to be addressed by any operating system for a multiprocessor machine, and we review the resulting solution approaches taken by a variety of commercial and research systems constructed during the last decade. Moreover, it should be apparent to the reader upon finishing this paper that many of these solution approaches are and have been applied to both parallel and distributed target hardware. This 'convergence' of technologies originally developed for parallel vs. distributed systems, by partially divergent technical communities and sometimes discussed with different terminologies is driven by recent technological developments: (1) multiprocessor engines, when scaled to hundreds of processors, can appear much like distributed sets of machines, and (2) distributed machines linked by high performance networks (especially local area networks or network devices derived from current ATM or even supercomputer routing technologies) are being increasingly used as parallel computing engines.

One self-imposed limitation of this survey is its focus on performance rather than reliability in parallel systems. Reliable systems are surveyed in several recent articles, including [237, 28, 149]. A second limitation of this survey is its treatment of operating system kernels rather than operating systems, thereby neglecting system functionalities like file systems, database support, network protocols, and others. This focus reflects an unfortunate lack of attention paid to such issues in many previous operating research projects and even in some commercial systems. Recent work is rapidly correcting such deficiencies. It includes industry efforts to offer concurrent I/O or file system support [114, 115] or even concurrent databases on parallel machines [195], work on communication protocols for high performance and parallel machines [110, 147], and research efforts addressing efficient file management on parallel machines [89, 31]. Such work is motivated by the intended use of parallel machines for commercial, large-scale data processing, by upcoming programs like NASA's EOS satellites which will generate Terabytes of data that have to be processed and re-processed for use in earth science applications [252], and it is motivated by the recent convergence of high performance computing and networking technologies resulting in large-scale, physically distributed, and heterogeneous parallel machines.

**Brief survey of multiprocessor hardware.** Several current textbooks in parallel computing provide good overviews of parallel machine architectures [111, 6, 233, 188]. For purposes of this paper, we briefly review some of the major types of parallel machines, eliding architectures for SIMD programs, functional programs, and systolic applications.

Depending on the coupling of processors and memory, multiprocessors may be broadly divided into two major categories:

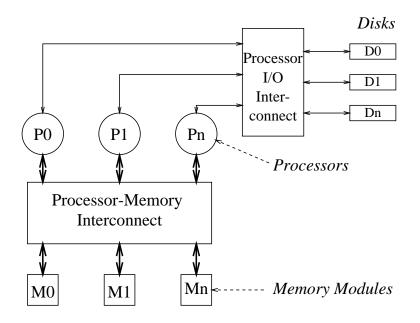

• Shared memory multiprocessors. In a shared memory multiprocessor, all main memory is accessible to and shared by all processors, as shown in Figure 1. Shared memory

Figure 1: Multiprocessor Architectures

multiprocessors are classified on the basis of the cost of accessing shared memory:

- 1. Uniform Memory Access (UMA) multiprocessors. In an UMA architecture, the access time to shared memory is the same for all processors. A sample UMA architecture is the bus based architecture of the Sequent multiprocessor [224], where a common bus links several memory modules to computing modules consisting of a cache shared by two processor elements, and I/O devices are attached directly to the bus.

- 2. Non-Uniform Memory Access (NUMA) multiprocessors. In a NUMA architecture, all physical memory in the system is partitioned into modules, each of which is local to and associated with a specific processor. As a result, access time to local memory is less than that to nonlocal memory. Sample NUMA machines are the BBN Butterfly parallel processor [130] and the Kendall Square Research supercomputer [195]. The BBN machines use an interconnection network to connect all processors to memory units, whereas the KSR machines use cache-based algorithms and a hierarchical set of busses for connecting processors to memory units. In both machines, I/O devices are attached to individual processor modules.

- *NO Remote Memory Access (NORMA) multiprocessors.* In this class of architectures, each processor has its own local memory that is not shared by other processors in the system. Hypercubes like the NCube multiprocessors, past *Intel iPSC* machines and current *Intel iSC* mesh machines [114, 115], the Thinking Machines CM-5 [246, 140], and workstation clusters are examples of non-shared memory multiprocessors. Workstation clusters differ from hypercube or mesh machines in that the latter typically offer specialized hardware for low-latency inter-machine communication and also for implementation of selected global operations like global synchronization, addition, or broadcast.

UMA architectures are the most common parallel machines, in part because most such machines are simply used as high throughput multiprogrammed, multi-user timesharing machines, rather than as execution vehicles for single, large-scale parallel programs. Interestingly, although all memory is accessed via a single shared bus, even UMA machines often have NUMA characteristics because individual processors access shared memory via local caches. Cache misses and cache flushing can result in effectively non-uniform memory access times. Furthermore, bus contention may aggravate variability in memory access times, and scalability is limited in that the shared global bus imposes limits on the maximum number of processors and memory modules it can accommodate.

A NUMA architecture addresses the scalability problem by attaching local memory to each processor. Processors directly access local memory and communicate with each other and with remote memory modules through an interconnection switch. One type of switch is an interconnection network consisting of multiple levels of internal nodes, where systems are scaled by addition of internal switch nodes, as in the BBN Butterfly multiprocessors [130, 64]. A second type of switch consists of a hierarchical set of busses [121, 195], where access times to remote memory depend on either the number of internal switch nodes on the access path between the processor and the memory or on the number of traversed system busses. Because a NUMA architecture allows a large number of processors in a single machine, many experimental, large-scale multiprocessors are NUMA machines, an example being the *IBM RP3* which was designed to contain up to 512 processors [45, 44], and the *KSR* machine again offering up to 512 processors.

NORMA multiprocessors are the simplest to design and build, and have become the architecture of choice for current supercomputers like the Intel Paragon [114, 115], recent Cray machines, and others. In the simplest case, a collection of workstations on a local area network constitutes a NORMA multiprocessor. A typical NORMA multiprocessor consists of a number of processors interconnected on a high speed bus or network; the topology of interconnection varies. One major difference between NUMA and NORMA multiprocessors is that there is no hardware support for direct access to remote memory modules. As a result, NORMAs are more loosely coupled than NUMA machines. However, recent advances in supercomputer technologies are leading to tradeoffs in remote to local memory access times for NORMA machines (e.g., roughly 1:500 for local vs. remote memory access times) that can approximate those achieved for shared memory machines like the KSR (roughly 1:100). This suggests that future NUMA or NORMA parallel machines will require similar operating system and programming tool support in order to achieve high performance parallelism.

A main component of a multiprocessor is its interconnection network. It connects the processors, the memory modules and the other devices in a system. An interconnection network, which may be static or dynamic, facilitates communication among processors and memory modules. A few sample interconnection networks are: time shared or common buses, crossbar switches, hierarchical switches, and multistage networks. The design, structure and performance of various interconnection networks have been reviewed in other literature [264, 111, 6, 233, 188] and are beyond the scope of this survey.

The variety of different kinds of multiprocessor architectures coupled with diverse application requirements have resulted in many different designs, goals, features, and implementations of multiprocessor operating systems, in university research projects and in the commercial domain. This paper examines a few such projects and commercial endeavors. The remainder of this paper is organized as follows. Section 2 briefly reviews a few common structuring techniques used to build an operating system. Section 3 discusses some key design issues. Finally, Section 4 examines a few sample multiprocessor operating system kernels developed for research and commercial purposes.

## 2 Structuring an Operating System

A multiprocessor operating system is typically large and complex. Its maintainability, expandability, adaptability, and portability strongly depend on its internal structure. Different techniques for structuring operating systems [25] are described in this section, along with a discussion of some of the effects of such structuring on the ease with which an operating system can be adapted for use with multiprocessor computing engines. The various structuring techniques described in this section are not mutually exclusive; several such techniques may be used in the construction of a single system.

While the bulk of this paper focusses on operating system kernels, this section must occasionally comment on the organization of the entire operating system. In this context, we define an operating system *kernel* as the basic operating system functionality permitting use of the processors, the main memory, the interconnection network, and the other devices of the parallel machine. Higher level operating system functionalities like user interfaces, file systems, database support, and networking are not unimportant, but their discussion is outside the scope of this paper, in part because their performance will be strongly affected by the performance attributes and basic functionality of the underlying system kernel.

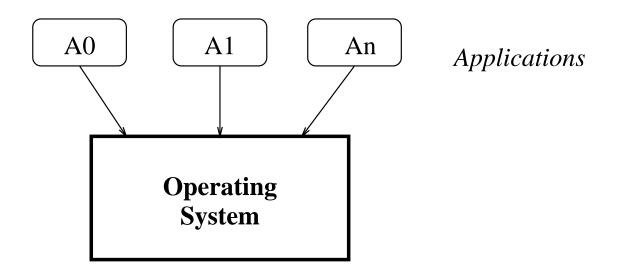

### 2.1 Monolithic Systems

Some operating systems such as Unix [196], OS/360 [166] and VMS [143] have been implemented with large, monolithic kernels insulated from user programs by simple hardware boundaries. No protection boundaries exist within the operating system kernel, and all communication among processes implementing higher level operating system functionality (e.g., file system daemons) happens through system-supplied shared memory or through explicit message-based communication constructs. It has been shown that the lack of a strong fire-wall within the large operating system kernel, combined with large kernel sizes and complexities, make such monolithic systems difficult to modify, debug and validate. The shallowness of the protection hierarchy makes the underlying hardware directly visible to a large amount of complicated operating system software. Monolithic systems are also extremely difficult to adapt for use in a distributed environment, and most such systems have no facilities that allow users to change some specific service provided by the operating system.

Recent experiences with the implementation of monolithic operating system kernels for parallel machines (e.g., the Sequent's or SGI's operating systems) have been confined to UMA machines. Attempts to build such systems for large-scale parallel machines like the RP3 have met with mixed success. As a result, more recent work in multiprocessor operating systems for machines like the RP3, the BBN Butterfly, and the KSR supercomputer have been based on Mach or on OSF Unix, both of which have smaller kernels and offer some facilities for kernel and operating system customization for different application domains and target machines (see Section 4.3 for a discussion of the Mach operating system's configuration support).

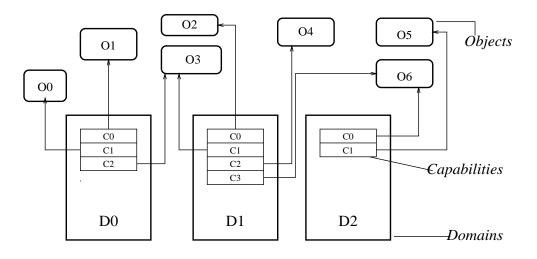

### 2.2 Capability Based Systems

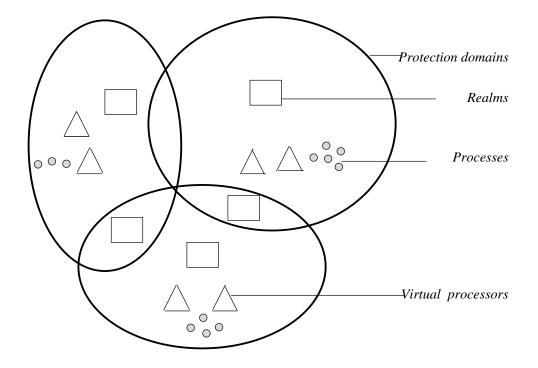

In a capability-based system [70], each accessible entity exists in its own protection domain, but all entities reside within a single name space. A capability is both a name and a set of access rights for an entity, and is managed by an underlying hardware or software kernel. A process is not allowed to reference an entity for which the process' current domain does not have a capability. An entity can be shared by more than one domain, but a process in one domain can access and manipulate such an entity only by invoking an access method for which the process has sufficient rights (according to its capability). Invocation across

Figure 2: Monolithic Systems

protection domains happens via a *protected procedure call*, in which a process in one domain having an appropriate *execute* capability, transfers control to a second domain, and executes entirely within the context of the second domain. Parameter passing is by reference between the caller and the callee.

Figure 3: Capability Systems

The implementation of capability based addressing has been carried out using both software and hardware techniques. A few sample software based systems are Hydra [258] and Cal/Tss [235]. CAP [179] and the Intel/432 [62] are examples of hardware based systems. Despite early favorable predictions, system builders have been largely unsuccessful in implementing and programming capability based systems which perform as well as machines based on more traditional memory reference models [132, 59]. This may be due to the fact that most early research and commercial systems focussed on the use of capabilities for enforcement of protection boundaries and system security characteristics, typically by enforcing the *Principle of Least Privilege*. This principle states that each program and each user of a system should operate using the least set of privileges necessary to complete a job [206]. Unfortunately, the principle's implementations often implied the *Principle of Least Performance*, which means that anything that was protected was also expensive to access, so that users attempted to avoid using a system's protection mechanisms, and implementors of commercial operating systems avoided using protection mechanisms to the maximum extent possible. It appears, however, that the extremely large address spaces offered by modern 64 bit architectures are beginning to reverse this trend, in part because it is evident that program debugging and maintainability require some fire-walls within the 64 bit addressing range potentially accessible to a single parallel program.

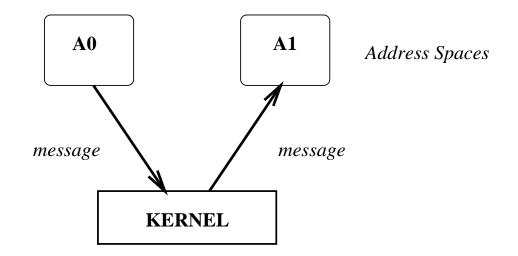

#### 2.3 Message Passing Systems

In a message passing system, a process always remains within its address space; communication among processes happens through message transfer via a communication channel. When a process in one address space requests a service from another address space, it creates a message describing its requirements, and sends it to the target address space. A process in the target address space receives the message, interprets it and services the request.

THE [72], Thoth [56], and Demos [16] are a few examples of the earliest message passing systems. The primary motivation behind the design of these systems was to decentralize the structure of an operating system running on a single computer. On the other hand, the motivation behind the latter message passing systems such as RIG [191], V [54], Accent [193], and various hypercube operating systems [205, 221] was to build an operating system on a structure of distributed computers.

Figure 4: Message Passing Systems

In contrast to the fine-grained protection of capability systems, network based message passing systems rely on a coarse-grained protection mechanism. Communication facilities based on messages transparently permit both local and remote communication. Local communication takes place between two address spaces on the same machine, whereas remote communication takes place between address spaces on different machines connected via a communication network.

A message passing system enforces modularity and is suitable for distribution. However, programs have to be manually structured in a paradigm that is foreign to the control and data

structuring mechanism of traditional "Algol-like" languages. Specifically, with message passing, data transfers have to be explicitly initiated whenever processes require communication. This gives programmers the opportunity to use application-specific knowledge to avoid unnecessary data transfers. However, message passing also requires that programmers use two entirely different mechanisms for access to memory: all local memory may be accessed using normal operations as done when accessing individual program variables, whereas all 'remote' memory must be accessed using message operations. Interestingly, recent research is beginning to address this dichotomy by providing a basic 'memory' abstraction for representation of both local and remote memory, and by addressing the potential performance penalties arising from providing this abstraction by 'weakening' the strong consistency requirements imposed on main memory [19, 145]. The resulting, weakened shared memory abstraction presented to programmers may be implemented efficiently because strong consistency and therefore, interprocessor communication is not required for all memory accesses. Other models of shared memory exploit programmer directives to reduce the cost of coherence maintenance [19], or they provide explicit primitives with which users can maintain application-specific notions of coherence of shared state [7] (see Section 3.2.2 for more information on this research).

One interesting lesson learned from current work on weakly consistent memories is that message passing and shared memory need not be different or mutually exclusive mechanisms. This may result in future operating systems that offer 'memory' abstractions or more strongly typed abstractions like 'shared queues' using object-like specification mechanisms. Such operating systems, therefore, might be structured as collections of cooperating objects, where object invocations may result in messages, in memory sharing, or in both, and where objects themselves may internally be structured as collections of cooperating objects or even as fragmented object [226, 57, 211, 159].

## 2.4 Language Based Mechanisms

**Single language systems.** CLU [148], Eden [134], Distributed Smalltalk [18], Emerald [125], and Linda [49] are a few examples of languages that integrate message based communication into the programming environment, either by defining all control structures in terms of messages, or by using messages as the basis for building "Algol-like" or entirely new control structures.

The advantages of a language based system are transparency and portability. References to local vs. remote objects are both handled transparently and automatically by the language's runtime system. In addition, the type system of the language can encourage optimizations that coalesce separate modules into one address space, while maintaining their logical separation. However, while such optimizations can alleviate certain performance problems with this approach, specific language primitives will inevitably impose performance penalties of which programmers must be aware in order to write efficient parallel programs. For example, the Ada rendezvous mechanism leads to well-known performance problems [43], the global addressing mechanisms and fixed language semantics of Linda can lead to inefficiencies concerning the update and access of remote information [211], and heap maintenance has been shown difficult for languages like Smalltalk [260, 186].

Another inherent problem with language based systems can be protection, where languagelevel typing mechanisms must be mapped to the protection mechanisms available in the underlying operating system [14, 254], which is not always easily done. In addition, any language based system will require all cooperating modules to be written in the same language, which precludes the use of mixed language environments. Furthermore, in order to guarantee the integrity of a system based on language-level decomposition, any executable code must be inspected by a trusted system entity to guarantee type-safety at runtime, essentially requiring access to its source code [25]. Finally, all language based systems will still require the availability of lower-level runtime system support for efficient program execution, as clearly apparent from current efforts to develop a threads-like common runtime system layer for both high performance Fortran and concurrent C++. It is precisely the structuring of such support that is the concern of this paper.

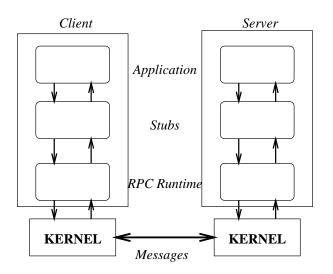

**Remote procedure calls.** Systems supporting Remote Procedure Calls (*RPC*) [30] occupy a middle ground between message based and single language systems. The use of RPC allows isolated components to be transparently integrated into a single logical system. In an RPC system, a procedure call interface hides the underlying communication mechanism that passes typed data objects among address spaces. Subsystems present themselves to one another in terms of interfaces implemented by servers. The absence of a single, uniform address space is compensated by automatic stub compilers and sophisticated runtime libraries [180, 110, 207] that transfer complex arguments in messages. RPC systems require that the data passed among cooperating modules be strongly typed; within a module, a programmer is free to mix languages, use weakly typed or untyped languages, violate typing if needed, and execute code for which source is not available [25].

Figure 5: Remote Procedure Call

RPC is used for both local and remote communication between address space. An RPC between address spaces on different machines is often referred to as a *cross-machine RPC* whereas an RPC between address spaces on the same machine is referred to as a *cross-address space RPC*.

The principal components of an RPC system are *clients*, *servers*, and *messages*. A server is an address space which contains the code and data necessary to implement a set of procedures which are exported to other address space. A client is an address space which requests a service from a server by sending an appropriate message [180].

## 2.5 Object-Oriented and Object-Supporting Operating Systems

Several ongoing projects are using or exploring the *object-oriented* paradigm for building operating systems. Such systems may be broadly classified as object-oriented or object-

supporting operating systems, depending on their internal structures and on the interfaces they provide to the user level [227, 198, 83].

**Object-Oriented Operating Systems (***OOOS***).** In an object-oriented operating system, an object encapsulates a system entity [156, 48]. An object-oriented language is primarily used to implement such an operating system [201]; the properties of the language such as data encapsulation, data abstraction, inheritance, polymorphism *etc.* are used to structure the system. An OOOS may or may not support objects at the user level. Examples of OOOSs are Choices [47] and Renaissance [202, 172].

**Object-Supporting Operating Systems (***OSOS***).** An object supporting operating system is not necessarily structured in an object-oriented fashion. However, it supports objects at the user level; the objects are typically language independent. Sample OSOSs are SOS [228], Cool [102], and CHAOS [213, 92, 91] for parallel machines, and Chorus [197] and Clouds [68] for distributed machines. OSOSs can further be classified into different groups depending on the kind of objects they support. In the *active-server* model of computation, objects are active entities containing threads of execution that service requests to the object [92, 91]. An OSOS supporting passive objects offers an *object-thread* model where a single thread of execution traverses all objects within an invocation chain [68, 128].

One use of object orientation in operating systems is to exploit type hierarchies to achieve operating system configuration (e.g., as done in Choices [47]) along with stronger notions of structuring than available in current systems. Another use of this technology is to use object based encapsulations of operating system services in order to represent operating system services internally in different ways, invisibly to services users. Examples of such uses are the internally parallel operating system servers offered in the Eden system [134] or in CHAOS [213, 92] and Presto [24, 23], the association of protection boundaries with certain objects as intended in Psyche [80], or the internally fragmented objects offered by Shapiro [227, 229, 98] for distributed systems, in 'Topologies' [211] for hypercube machines, and in 'Distributed Shared Abstractions' [57] for multiprocessor engines.

Unresolved issues with object-oriented operating systems include the efficient representation of object invocations, where it has become clear that 'not all invocations are equal', ranging from rapid unreliable invocations useful in real-time multiprocessor applications [213, 92] to reliable multicast invocations required for certain distributed programs [103]. In addition, as with remote procedure calls, it is unclear what levels of machine and language support are required for efficient implementation of object invocations (e.g., for parameter marshaling [103] or for crossing protection boundaries [258, 80]). However, object-oriented operating systems are likely to become increasingly important in part (1) because of the wide range of parallel architectures (or even sequential machines – ranging from digital pages to workstations) to be supported by future parallel operating systems and (2) because of the increasing importance of object-oriented languages like C++. It is likely that object-oriented operating systems will be constructed using the micro-kernel operating system structuring technique explained in Section 2.7.

## 2.6 Vertical and Horizontal Organizations

Some researchers have identified two broad classes of organization of operating system kernels referred to as horizontal and vertical organization [80]. These alternatives roughly correspond to the message-based and procedure-based organizations respectively [133].

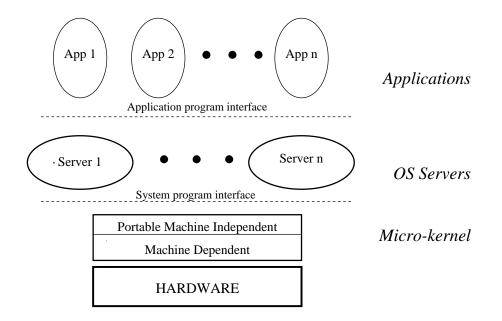

Figure 6: Micro-kernel based operating system

**Vertical Organizations.** In a vertical kernel, there is no fundamental distinction between a process in the user space and a process in the kernel. A user process enters the kernel via a trap when required, performs a kernel operation, and returns to user space. A kernel resource is represented by a data structure shared among processes. The vertical organization presents a uniform model for the user and the kernel level processes and closely mimics the hardware organization of a UMA multiprocessor. Most Unix [196] kernels are vertically organized.

**Horizontal Organizations.** In a horizontal kernel, each major kernel resource is represented by a separate kernel process (or thread), and a typical kernel operation requires communication among the set of kernel processes that represent the resources needed by the operation. The horizontal organization leads to a compartmentalization of the kernel in which all synchronization is subsumed by message passing. The horizontal organization closely mimics the hardware organization of a distributed memory multicomputer. Demos [16] and Minix [239] are examples of horizontal kernels.

## 2.7 Micro-kernel Based Operating Systems

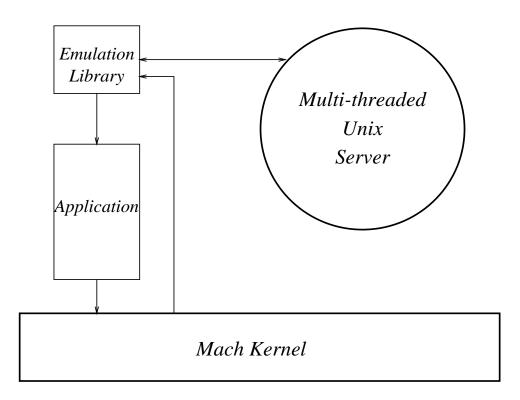

Micro-kernel based operating systems are structured as a collection of system servers running on top of a minimal kernel (see Figure 6). The micro-kernel itself only implements the lowestlevel (mostly hardware dependent) functions of an operating system. Such primitive functions include task and thread management, interprocess communication/synchronization, lowlevel memory management, and minimal device management (I/O). All higher level operating system services are implemented as user-level programs. Therefore, applications must use cross-address space RPC to interact with most operating system services. This implies that the performance of inter-process communication (IPC) mechanism plays a critical role in the performance of such operating systems [20].

The primary characteristic of micro-kernel based operating systems is modularity, thereby hoping to improve system extensibility, portability, reconfigurability, and improved support for distribution [251, 93, 92]. Improvements in distribution, extensibility, and reconfigurability [175] result from the separation of system components from each other, and from the use of message passing as the communication mechanism among them [251]. As a result, new services can be added (as new servers) or an existing server can be replaced by another without altering the existing components or the micro-kernel itself. Unlike large monolithic systems, such architectures also localize the hardware-dependent portions of the operating system inside the kernel, thereby potentially improving operating system portability. Furthermore, the use of common underlying services provides support for the coexistence and interoperability of multiple operating system environments on a single host as user-level programs [32]. Mach [32], Chorus [197], KeyKOS [42], QNX [106], and BirLiX [208] are a few examples of micro-kernel based operating systems.

### 2.8 Application-specific Operating Systems

Many application domains impose specific requirements on operating system functionality, performance, and structure. One blatant example of such requirements comes from the realtime domain, where application software and operating system support can be so intertwined that many systems may be better described as consisting of *operating software* – combined application software and operating system support functions – rather than as application software and an underlying operating system. This is because in contrast to other parallel or distributed application software, the control software of real-time systems cannot be termed *reliable* unless it exhibits two key attributes [209]: (1) computations must complete within well-defined timing constraints, and (2) programs must exhibit predictable behavior in the presence of uncertain operating environments [210, 27]. Operating software, then, must have direct access to the underlying resources typically controlled by the operating system, and for complex applications, it must deal with uncertainty in operating environments by even permitting programs or operating system components to *adapt* [215, 129] (i.e., change at runtime) in performance [209] and functionality during system execution [210, 213, 26, 96].

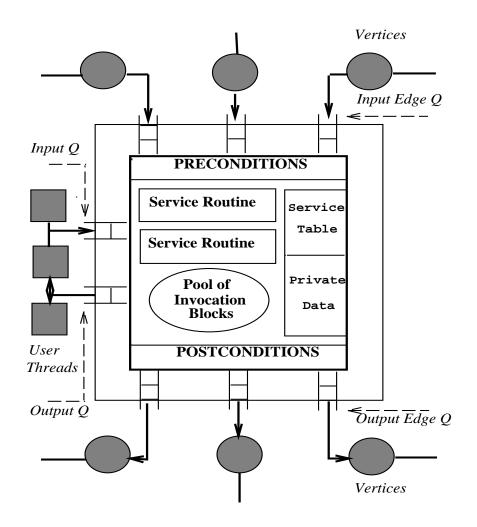

While many embedded real-time operating systems are offering functionality akin to multiuser systems, they do not impose any restrictions on resource use and reservation by application programs. For instance, in the CHAOS and CHAOS<sup>arc</sup> operating systems [96, 213, 92], operating software implementing either application or operating system functionality consists of a number of autonomous objects, each providing a number of operations (entry points) that can be invoked by other objects. Such functionality appears no different from what is offered by other object-oriented operating systems. However, addressing the requirements of real-time programs, CHAOS<sup>arc</sup> object invocations range from reliable invocations that maintain parameters and return information (or even communication 'streams' [213]) to invocations that implement unreliable 'control signals' or 'pulses' [213, 253]. Furthermore, invocation semantics can be varied by attachment of real-time attributes like delays and deadlines, where deadline semantics may vary from quaranteed deadlines, which are hard deadlines that must not be missed to *weak deadlines* [154], which specify that partial or incomplete results are acceptable when the deadline is missed. The resulting direct access to resources is a characteristic such real-time operating systems share only with certain single-user operating systems for parallel machines. On the other hand, system configurability is a property CHAOS<sup>arc</sup> shares with many current high-performance operating systems, including the Synthesis kernel [163, 162], the Psyche system and its related research [219, 168], Presto [24, 23], and others [24, 23, 52].

Other examples of application-dependent operating system structures occur for database systems, where an operating system's I/O facilities and networking facilities may be determined or at least strongly affected by the primary application running on this system: a large-scale database performing transaction processing [231].

## **3** Design Issues

The basic functionality of a multiprocessor operating system must include most what is present in uniprocessor systems. However, complexities arise due to the additional functional capabilities in multiprocessor hardware and more importantly, due to the extreme requirements of performance imposed on the operating system. Namely, since one main reason for using parallel hardware is to improve the performance of large-scale application programs, an operating system or system constructs that perform poorly are simply not acceptable [11, 89]. Specific problems to be addressed concerning performance include protection in very large address spaces, deadlock prevention, exception handling for large-scale parallel programs, the efficient representation of asynchronous active entities like processes or threads, the provision of alternative communication schemes and synchronization mechanisms, and resource scheduling like process assignment to different processors and data placement in physically distributed memory [214], and finally, the parallelization of the operating system itself, again in order to provide scalable performance for varying application requirements [89, 109, 270].

A second major reason for using a multiprocessor system is to provide high reliability, and graceful degradation in the event of failure. Hence, several multiprocessor systems have been constructed and designed for improved fault tolerance. Such systems will not be discussed in this survey (see [28] for a survey of fault tolerant operating systems).

The following sections focus on design issues that concern operating system kernels or micro-kernels and therefore, the basic functionality that must be offered by multiprocessor operating systems, including processor management and scheduling, main memory management, and interprocess communication and synchronization.

## 3.1 Processor Management and Scheduling

The classic functions of an operating system include creation and management of active entities like processes. The effectiveness of parallel computing depends on the performance of the primitives offered by the system to express parallelism. If the cost of creating and managing parallelism is high, even a coarse-grained parallel program exhibits poor performance. Similarly, if the cost of creating and managing parallelism is low, even a fine-grained program can achieve excellent performance.

### 3.1.1 Heavyweight Processes to Lightweight Threads

One way to express parallelism is by using "Unix-like" processes sharing parts of their address spaces. Such a process consists of a single address space and a single thread of control. Kernels supporting such processes do not distinguish between a thread and its address space; they are sometimes referred to as *heavyweight* threads. The parallelism expressed using heavyweight threads is coarse-grained and is too inefficient for general purpose parallel programming for the following reasons:

- Since the kernel treats a thread and its address space as a single entity, threads and address space are created, scheduled, and destroyed together. As a result, the creation and deletion of heavyweight threads are expensive.

- Reallocating a processor to a different address space (context switch) is expensive. There is an initial scheduling cost to decide the address space to which the processor should be reallocated. Next, there is a cost for updating the virtual memory mapping registers and transferring the processor between address spaces. Finally, there is a long term cost associated with cache and TLB performance due to the address space change [169].

Hence, in many contemporary operating system kernels, address spaces and threads are decoupled, so that a single address space can have more than one execution threads. Such threads are referred to as *middleweight* threads or *kernel-level* threads when they are managed by the operating system kernel (POSIX Pthreads [185]). The advantages of middleweight threads are:

- The kernel can directly schedule an application's thread on the available physical processors.

- Kernel-level threads offer a general programming interface to the application.

Kernel-level threads also exhibit some problems that can make them impractical for use in fine-grained parallel programs [25]:

- The cost of generality of kernel-level threads is not acceptable to fine grained parallel applications. For example, saving and restoring floating point context in a context switch are expensive and may be unnecessary for a specific application program.

- A relatively costly protected kernel call is required to invoke any thread management operation, including thread synchronization. For example, many programs would rather have direct access to the hardware's synchronization operations.

- A single model represented by one style of kernel-level thread is unlikely to have an implementation that is efficient for all parallel programs.

To address the above problems with kernel-level threads, system researchers have turned to *user-level* threads, also known as *lightweight* threads. User-level threads are managed by runtime library routines linked into each application. A thread management operation does not require an expensive kernel call. Furthermore, lightweight threads enable an application program to use a thread management system, most appropriate to the problem domain. Mach Cthreads [60, 173, 212], the University of Washington threads [165, 9], SunOS LWP and threads [113, 127, 189], are a few popular lightweight thread implementations.

A lightweight thread generally executes in the context of a middleweight or a heavyweight thread. Specifically, the threads library schedules lightweight threads on top of middleweight or heavyweight threads, which in turn are scheduled by the kernel on the available physical processors. Such a *two-level scheduling* policy has some inherent problems:

- User level threads, typically, do not have any knowledge of kernel events (*e.g.*, processor preemption, I/O blocking and resuming, *etc.*). As a result, the application library cannot schedule a thread on a "just idle" processor.

- When the number of runnable kernel-level threads in a single address space is greater than the number of available processors, kernel-level threads must be multiplexed on the available processors. This implies that user-level threads built on top of kernel-level threads are actually scheduled by the kernel's thread scheduler, which has little or no knowledge of the application's scheduling requirements or current state [9].

Problems with multi-level scheduling arise from the lack of information flow between different scheduling levels. Anderson et al. in [9] attempt to solve these problems for two-level scheduling by:

1. Explicit vectoring of kernel events to the user level thread scheduler, using upcalls called *scheduler activations*<sup>1</sup>, and by

<sup>&</sup>lt;sup>1</sup>Scheduler activations are defined to be entities similar to kernel-level threads. One crucial distinction between scheduler activations and kernel level threads is that scheduler activations are not scheduled by the kernel. The kernel maintains the invariant that there are always exactly as many runnable scheduler activations as there are processors assigned to each address space.

2. notifying the kernel of user-level events affecting processor allocation.

Tucker and Gupta [249] propose a similar solution which dyanamically controls the number of processes used by applications. This scheme is discussed in details in Section 3.1.3. Similarly, Marsh et al. in [161] propose a set of kernel mechanisms (incorporated in the Psyche operating system) required to implement "first-class user-level" threads addressing the above problem. These mechanisms include shared kernel/user data structures (for asynchronous communication between the kernel and the user), software interrupts (for events that might require action on the part of a user-level scheduler), and a scheduler interface convention that facilitates interactions in user space between dissimilar kinds of threads (see section 4.5 for more on Psyche user-level threads).

A recent paper by Anderson et al. [10] also explores data structure alternatives when implementing user-level thread packages. Alternate implementations are evaluated in performance for thread run queues, idle processor queues, and for spinlock management. We are not aware of general solutions to the multi-level scheduling problem, other than the actual exchange or configuration of the operating system's threads scheduler by application programs, as often done in real-time systems [216].

#### 3.1.2 Scheduler Structures

As with other operating system services for parallel machines, schedulers themselves must be structured to be scalable to different size target machines and to different application requirements. Mohan in his PhD thesis [170, 89] addresses this problem by designing a flexible run-queue structure, where scheduler run-queues can be configured such that any number of queues may be used by any number of processors. A similar approach to run-queue organization is taken in the Intel 432's iMAX operating system [63]. Recent work on real-time schedulers for parallel systems is also considering the effects of sharing alternative policylevel scheduling information on parallel scheduler performance [270]. Beyond this work, scheduler structuring remains largely unexplored, but should receive increased attention in operating systems for large-scale parallel machines like the Intel Paragon multiprocessor.

### 3.1.3 Scheduling Policies

A scheduling policy allocates available time and processors to a job or a process statically or dynamically [153]. Processor load balancing<sup>2</sup> is considered to be a part of a scheduling policy [232]. Basic theoretical results on static process scheduling on parallel machines show that the scheduling problem is NP-hard; static algorithms minimizing average response time include those described in [164] and [39]. Other scheduling algorithms appear in [267] and [141]. In this section, we focus on dynamic scheduling [164], and on scheduling for shared memory machines, where variations in distances between different processors on the parallel machine [39, 214] are not considered.

**Static and Dynamic Scheduling:** A static scheduler makes a one time decision per job regarding the number of processors to be allocated. Once decided, the job is guaranteed to have exactly that number of processors whenever it is active. A static scheduler offers low runtime scheduling overhead [78], but it also assumes a stable parallel application. This is a reasonable assumption for many large-scale scientific applications in which parallelism is derived by decomposition of regular data domains [204]. Recent work, however, is focussing more on dynamic scheduling for two reasons: (1) because most complex large-scale parallel applications over time,

$<sup>^{2} \</sup>rm Processor load balancing concerns the dynamic distribution of processing loads among the processors of the parallel machine.$

so that a static processor allocation rapidly becomes inefficient and (2) large-scale parallel machines are often used in multi-user mode, so that scheduling must take into account the requirements of multiple parallel applications sharing a single machine [158, 157, 225, 65].

J. Zahorjan and C. McCann compare the performance of static and dynamic schedulers for multi-user workloads. Their results include [267]:

- Independent of workload and overall system load, dynamic scheduling performs best when context switch overheads are small.

- The advantage of dynamic scheduling at low context switch costs increases with larger and more rapid changes in the parallelism exhibited by a workload.

- Dynamic scheduling performs increasingly well relative to the static counterpart as system load increases.

- In terms of average response time, dynamic scheduling dominates static scheduling for almost all overhead (context switch) values.

The dynamic policy occasionally exhibits a performance penalty when overhead values are very large. One reason for such performance degradation is a possible high rate of processor reallocation. Hence, some researchers have suggested to dampen the rate of processor allocation and release, thereby reducing the rate of "useless processors exchange" [267]. However, such a modification to the dynamic policy was found to be detrimental to performance [267].

As for uniprocessors, multiprocessor schedulers can be classified as preemptive or nonpreemptive schedulers. A scheduler can also be classified according to its scheduling granularity, which is determined by the executable unit being scheduled (For example, schedulers differ in that they may schedule individual or groups of processes). A few well accepted multiprocessor scheduling policies are reviewed next [141].

**Single Shared Ready Queue:** Research addressing UMA multiprocessors has typically assumed the use of a single ready queue shared by all processors. With this queue, policies like First Come First Served (FCFS) or Shortest Job First (SJF) are easily implemented, and have been evaluated in the literature. More interesting to us are schedulers and scheduling policies directly addressing the primary requirement of a parallel program: if performance improvements are to be attained by use of parallelism, then the program's processes must be scheduled to execute in parallel.

**Coscheduling:** The goal of coscheduling (or gang scheduling) is to achieve a high degree of simultaneous execution of processes belonging to a single job. This is particularly useful for a parallel application with cooperating processes that communicate frequently. A coscheduling policy schedules the runnable processes of a job to run simultaneously on different processors. Job preemption implies the simultaneous preemption of all of its processes. Effectively, the system context switches between jobs.

Ousterhout proposed and evaluated three different coscheduling algorithms in his PhD thesis [183]: matrix, continuous and undivided. In the matrix algorithm, processes of arriving jobs are arranged in a matrix with p columns and a certain number of rows, where p is the total number of processors in the system. The arrangement of jobs is such that all the processes in a job reside in a same row. The scheduling algorithm uses a round-robin mechanism to multiplex the system between different rows of the matrix, so that all the processes in a row are coscheduled.

A problem with the matrix algorithm is that a hole in the matrix may result in a processor being idle even though there are runnable processes. The continuous algorithm addresses this problem by arranging all processes in a linear sequence of activity slots<sup>3</sup>. The algorithm considers a window of p consecutive positions in the sequence at a particular moment. When a new job arrives, the window is checked to see if there are enough empty slots to satisfy its requirements. If not, the window is moved one or more positions to the right, until the leftmost activity slot in the window is empty but the slot just outside the window to the left is full. This process is repeated until a suitable window position is found to contain the entire job or the end of the linear sequence is reached. Scheduling consists of moving the window to the right at the beginning of each time slice until the leftmost process in the window is the leftmost process of a job that was not coscheduled in the previous time slice.

The most serious problem with the continuous algorithm is analogous to external fragmentation in a segmentation system. A new job may be split into fragments, which can result in unfair scheduling for a large, split jobs vs. small contiguous jobs. Ousterhout addresses this issue by designing an undivided algorithm, which is identical to the continuous algorithm except that all of the processes of each new job are required to be contiguous in the linear activity sequence. Leutenegger & Vernon [141] slightly modify the undivided algorithm to eliminate some of its performance problems: when a job arrives, its processes are appended to the end of a linked list of processes. Scheduling is done by moving a window of length equal to the number of processors over the linked list. Each process in the window receives one quantum of service on a processor. At the end of the quantum, the window is moved down the linked list until the first slot of the window is over the first process of a job that was not completely coscheduled in the previous quantum. When a process within the window is not runnable, the window is extended by one process and the non-runnable process is not scheduled. All processors that switch processes at the end of a quantum do so at the same time. A second algorithm modification improves expected performance for correlated workloads. This modification is in the movement of the window. At the end of each quanta, the window is only moved to the first process of the next job, even if the job was coscheduled in the previous time slice.

Round Robin (RR) Scheduling: Two versions of RR scheduling exist for multiprocessors. The first version is a straightforward extension of the uniprocessor round robin scheduling policy. On arrival of a job, its processes are appended to the end of the shared process queue. A round robin scheduling policy is then invoked on the process queue. The second version uses jobs rather than processes as the scheduling unit. The shared process queue is replaced by a shared job queue. Each entry of the job queue contains a queue holding its processes. Scheduling is done round robin on the jobs. The job in the front of the queue receives pquanta of size q, where p is the number of processors in the system and q is the quantum size. If a job has fewer processes than p, then the total quanta size, which is equal to pq, is divided equally among the processes. If the number of processes in a job exceeds p, then there are two choices. The first choice is same as the previous case, *i.e.*, divide the total quanta size pq equally among all processes. The other choice is to choose p processes from the job in a round robin fashion, each process executing for one quanta. The first alternative has more scheduling overhead than the second one.

In [249], the authors observe that the performance of an application worsens considerably when the number of processes in the system exceeds the total number of processors. They attribute this decreased performance to several problems:

• A process may be preempted while inside a spinlock-controlled critical section, while the other processes of the same application "busy wait" to enter the critical section. This

<sup>&</sup>lt;sup>3</sup>In [183], Ousterhout defines an *activity slot* as a slot to which an activity (or a process) may be assigned. Scheduling consists of selecting one activity slot in each processor; the assigned activity is executed by the processor. The collection of activity slots is referred to as the activity space. The three algorithms, described here, assume that no job contains more than p (number of processors) processes. 16

problem is particularly acute for fine-grain parallel programs. Identical problems arise when programs' processes are engaged in producer/consumer relationships.

- Frequent context switches occur when the number of processes greatly exceeds the number of processors.

- When a processor is interleaved between multiple address space, cache misses can be a major source of performance degradation [245].

Careful application design and coscheduling may handle the problems associated with spinlock-controlled critical sections and those with producer-consumer processes, but they do not address performance degradation due to cache corruption or frequent context switches. A more direct solution is proposed by Zahorjan et al. [265], who describe a thread scheduler that avoids preempting processes inside critical sections. In contrast, Edler et al. [79] propose an approach combining coscheduling and preemption avoidance for critical sections. Multiple processes are combined to form a group. The scheduling policy of a group can be set so that either all processes in the group are scheduled and preempted simultaneously, or individual processes are scheduled and preempted normally, or processes in the group are never preempted. An individual process may choose to override its group scheduling policy. This policy is flexible, but it leave specific solutions to the critical section problem to user code.

The problems of cache corruption and context switch frequency are addressed by Lazowska and Squillante [135], who evaluate the performance of several multiprocessor scheduling policies based on the notion of processor affinity. A process's processor affinity is based on the contents of the processor's cache. The basic policy schedules a process on a processor on which it last executed hoping that a large percentage of its working set is still present in the processor's cache. Since the policy inherently discourages process migration, it may lead to severe load imbalance. The authors of [135] address this issue by proposing a variation on the basic policy which successfully reduces the cache corruption problem.

Similarly, affinity (for local memory) also plays a vital role in scheduling processes in a NUMA machine; the context of a process resides mostly near the processor on which the process executed last.

Vaswani and Zahorjan [250] also study the effect of cache affinity on kernel processor scheduling discipline for multiprogrammed, shared memory multiprocessors and conclude that the cache effects due to processor reallocation can be significant. However, their experiments demonstrate that affinity scheduling has negligible effect on performance for current multiprocessors. Finally, they conclude that even on future, faster machines, a scheduling policy based on dynamic reallocation of processors among jobs outperforms a more static, equipartition policy.

Tucker and Gupta [249] propose a different solution for reducing the frequency of context switches and for reducing cache corruption, which is explained next.

**Dynamic Partitioning:** The dynamic partitioning [187, 73] (also known as *Process control* with processor partitioning) policy proposed by Tucker and Gupta [249] has the goal of minimizing context switches, so that less time is spent rebuilding a processor's cache. Their approach is based on the hypothesis that an application performs best when the number of runnable processes is the same as the number of processors. As a result, each job is dynamically allocated an equal fraction of the total number of processors, but no job is allocated more processors than it has runnable processes. Each application program periodically polls a scheduling server to determine the number of process suspends some of its processes,

if possible. If the ideal number is greater than the actual number, a process wakes up a previously suspended process. This policy has limited generality since it requires interactions between user processes and the operating system scheduler, and since it requires that user programs are written such that their processes can be suspended and woken up during program execution.

**Hand-off Scheduling:** A kernel level scheduler that accepts user hints is described in [36]. Two kinds of hints exist:

- Discouragement hints: A discouragement hint is used to discourage the scheduler to run the current thread. A discouragement hint may be either *mild*, *strong*, or *weak*. David Black in [36] discusses a scheduler that accepts discouragement hints.

- Hand-off hints: A hand-off hint is used to suggest the scheduler to run a specific thread. Using a hand-off hint, the current thread hands off the processor to another thread without intermediate scheduler interference. Such schedulers are better known as *hand-off* schedulers.

two experiments with scheduling hints are described in [36], and it is shown that scheduling hints can be used to improve program performance. Hand-off scheduling has been shown to perform better when program synchronization is exploited (e.g., the requester thread hands off the processor to the holder of the lock) and when interprocess communication takes place (e.g., the sender hands the processor off to the receiver).

In [101], Gupta et al. use a detailed simulation study to evaluate the performance of several scheduling strategies. These include regular priority scheduling, coscheduling or gang scheduling, process control with processor partitioning, hand-off scheduling, and affinity based scheduling [248]. In addition, tradeoffs between the use of busy waiting and blocking synchronization primitives are explored, in conjunction with their interactions with different scheduling strategies. A key focus of the study is the impact of different scheduling strategies on the caching behavior of an application. Results demonstrate that in situations where the number of processes exceeds the number of processors, regular priority-based scheduling in conjunction with busy-waiting synchronization primitives results in extremely poor processor utilization. In such cases, the use of blocking synchronization primitives improves performance significantly. Process control and gang scheduling strategies are shown to offer the highest performance, and their performance is relatively independent of the synchronization methods used. However, for applications that have sizable working sets that fit into the cache, process control performs better than gang scheduling. For the applications considered<sup>4</sup>, the performance gains due to hand-off scheduling and processor affinity are shown to be small.

In [266] the authors study the effects of two environmental factors, multiprogramming and data-dependent execution times, on spinning overhead of parallel applications, and how the choice of scheduling discipline can be used to reduce the amount of spinning in each case. Specifically, they conclude that decisions about how to allocate processors to jobs and how to schedule the threads of a job on its processors must be made cooperatively. Furthermore, for the range of workloads and systems considered, the difference in mean performance between synchronization via spinning vs. blocking is found to be very little. They also compare the static scheduling policy to both fixed and variable self-scheduling policies when the number of independent tasks exceeds the number of processors available and conclude that the variable self-scheduling policy provides good overall performance and is the most robust with respect to overhead costs.

Ongoing research also addresses the development of schedulers for specific application domains or for specific target machines. One such area is real time systems. In a real time

<sup>&</sup>lt;sup>4</sup>The applications considered are a particle-based simulator called MP3D, LU-decomposition on dense matrices, a parallel implementation of Goldberg and Tarjan's Maxflow algorithm [94], and a highly optimized block-based parallel algorithm for multiplying two matrices.

system, a scheduling policy must satisfy timing constraints such as deadlines, earliest start times, *etc.* of an incoming job. Before a job is assigned one or more physical processors, the scheduler checks whether the system can satisfy the job's timing constraints. This analysis is known as *schedulability analysis*. Schedulability analysis and scheduling for real time systems [53, 269, 37, 108, 150, 71, 268] are active areas of research and are not within the scope of this paper.

## 3.2 Memory Management

Memory management for UMA multiprocessors is conceptually similar to that for multiprogrammed uniprocessors. As mentioned earlier, in an UMA architecture, memory access times are equal for all processors. However, the underlying architecture typically supports some degree of parallelism in global memory access. As a result, even for UMA machines, operating system writers must exploit the available hardware parallelism when implementing efficient memory management. More interesting problems arise for NUMA and NORMA machines.

For early research on memory management in parallel machines, including the implementation of physically distributed, internally parallel memory managers, the reader is referred to [119, 120, 89], which present the innovative designs and structures of memory or object managers for the Cmmp and Cm\* multiprocessor systems. Recent research has focussed primarily on page management, namely, on memory management in the context of virtual memory systems implemented for parallel machines.

#### 3.2.1 Shared Virtual Memory

A typical virtual memory system manages a memory hierarchy consisting of a cache, uniformly accessible primary memory, and significantly slower secondary memory. Unlike the traditional approach of a three level store, the Accent operating system [84], supports *a single level store*, in which primary memory acts as a cache of secondary storage. Filesystem data and runtime allocated storage are both implemented as disk-based data objects. Copies of large messages are managed using *shadow paging* techniques. Other contemporary systems like the IBM System 38 and Apollo Aegis also use the single level store approach, but limit its application to the management of files.

A central feature of Accent is the integration of virtual memory and communication. Large amounts data can be transmitted between processes with high performance using memory mapping techniques. As a result, client and server processes can exchange potentially large data objects like files without concern for the traditional data copying cost of message passing. In effect, Accent carries into the domain of message passing systems the notion that I/O can be performed through virtual memory management.

The design of the Mach system's memory management is largely derived from the Accent system [194, 1, 263, 262]. Its single level store is attractive because it can simplify the construction of an application program by allowing programmers to map a file into the address space of a process, and because it can improve program performance by permitting file data to be read directly into physical memory pages rather than into intermediate buffers managed by the operating system. Furthermore, because physical memory is used to cache secondary storage, repeated references to the same data can often be made without corresponding disk transfers. The design and implementation of the Mach memory management is discussed in detail in Section 4.3 below.

Memory management services and implementations are generally dependent on the operating system<sup>5</sup> as well as the underlying machine architecture. Some of the current research

<sup>&</sup>lt;sup>5</sup>For example, in real-time executives, memory management services are simple and primitive. General purpose operating systems such as Unix allow protected address spaces to co-exist on the machine hardware. Some distributed systems support distributed memory schemes.

has focussed on designing memory management functionalities and interfaces which are independent of the machine architecture and the operating system kernel. For example, the Mach operating system implements virtual memory management which is machine and operating system independent [194]. The machine-dependent portion of Mach's virtual memory subsystem is implemented as a separate module. All information important to the management of the virtual memory is maintained in machine-independent data structures and machine-dependent data structures contain only the mappings necessary to run the current mix of programs [194] (See Section 4.3 for more on the implementation of the Mach virtual memory management). Similarly, in [2], the authors present the design and the implementation of a scalable, kernel-independent, Generic Memory Management Interface (GMI) (for the Chorus [197] nucleus) which is suitable for various architectures (e.g. paged and/or segmented) and implementation schemes.

Some operating systems [84] allow applications to specify the protection level (inaccessible, read-only, read-write) of pages, and allow user programs to handle protection violations. In [12], the authors survey several user-level algorithms that make use of page-protection techniques, and analyze their common characteristics, in an attempt to identify the virtual-memory primitives the operating system should provide to user processes. The survey also benchmarks a number of systems to analyze a few operating systems' support for user-level page-protection techniques.

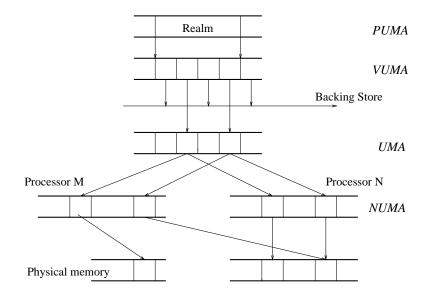

#### 3.2.2 NUMA and NORMA Memory Management

Most early NUMA multiprocessor systems did not offer virtual memory support. However, recent NUMA or NORMA parallel machines like the Thinking Machines CM-5, the Kendall Square KSR, and the Intel Paragon, and all UMA operating systems routinely offer virtual memory.

A NUMA multiprocessor organization leads to memory management design choices that differ markedly from those that are common in systems designed for uniprocessors or UMA multiprocessors. Specifically, NUMA machines like the BBN Butterfly do not support cache or main memory consistency on different processors' memory modules. Such consistency is guaranteed only for local memory and caches (i.e., for non-shared memory), or it must be explicitly enforced for shared memory by user- or compiler-generated code performing explicit block or page moves [194, 262]. As a result, NUMA architectures implementing a shared memory programming model typically expose the existing memory access hierarchy to the application program, as done in BBN's Uniform System [247]. Motivations for exposing such information include:

- 1. Giving programmers the ability to minimize relatively expensive remote vs. less expensive local memory references (i.e., maximize program locality [120]), and

- 2. permitting programmers to avoid several forms of potential contention (switch or memory contention) caused by a large number of remote memory references [261].

Recent parallel NUMA architectures like the Kendall Square multiprocessor offer consistent global virtual memory. However, the performance reasons for exposing programmers to the underlying machine's NUMA properties persist, leading the system designers to include hardware instructions for page prefetches and poststores [112].

Research in memory management for parallel machines has focussed on designing techniques for NUMA multiprocessors that relieve programmers from the responsibility of explicit code and data placement. Realizing that the problem of memory management is similar to the problem of cache management and consistency for UMA multiprocessors, the Mach operating system's UMA implementation of memory management [194, 262] attempts to minimize the amount of data-copying and replication by using page *copy-on-write* and similar techniques for reduction of data movement. In essence, the operating system is exploiting the fact that the sharing of "read-only" data on a multiprocessor does not require the allocation of multiple private copies; different processes can remotely access a single copy located with the writing process. On NUMA machines, however, extra data movement in terms of page replication and migration may result in improved performance, due to decreased page access times for locally stored pages and due to the elimination of possible switch or memory contention for access to shared pages, as demonstrated by specific measurements on the BBN Butterfly multiprocessor reported in several sections below, including Section 4.5.

We briefly discuss several memory management algorithms for NUMA multiprocessors. Various multiprocessor operating systems such as Mach, Psyche, and PLATINUM use a variation or a mix of these algorithms.

The algorithms described below are categorized by whether they migrate and/or replicate data [234, 271]. One algorithm migrates data to the site where it is accessed in an attempt to exploit locality in data accesses and decreases the number of remote accesses. Two other algorithms replicate data so that multiple read accesses can happen at the same time using local accesses.